- Sản phẩm khuyến mại

Công Ty TNHH TM và DV Anasa 087.884.2345 - ĐT Zalo 0941344233

Sản Phẩm Khuyến Mại

229.000₫

249.000₫

-

8%

35.000₫

42.000₫

-

17%

Sản Phẩm Mới

- Tất Cả Sản Phẩm

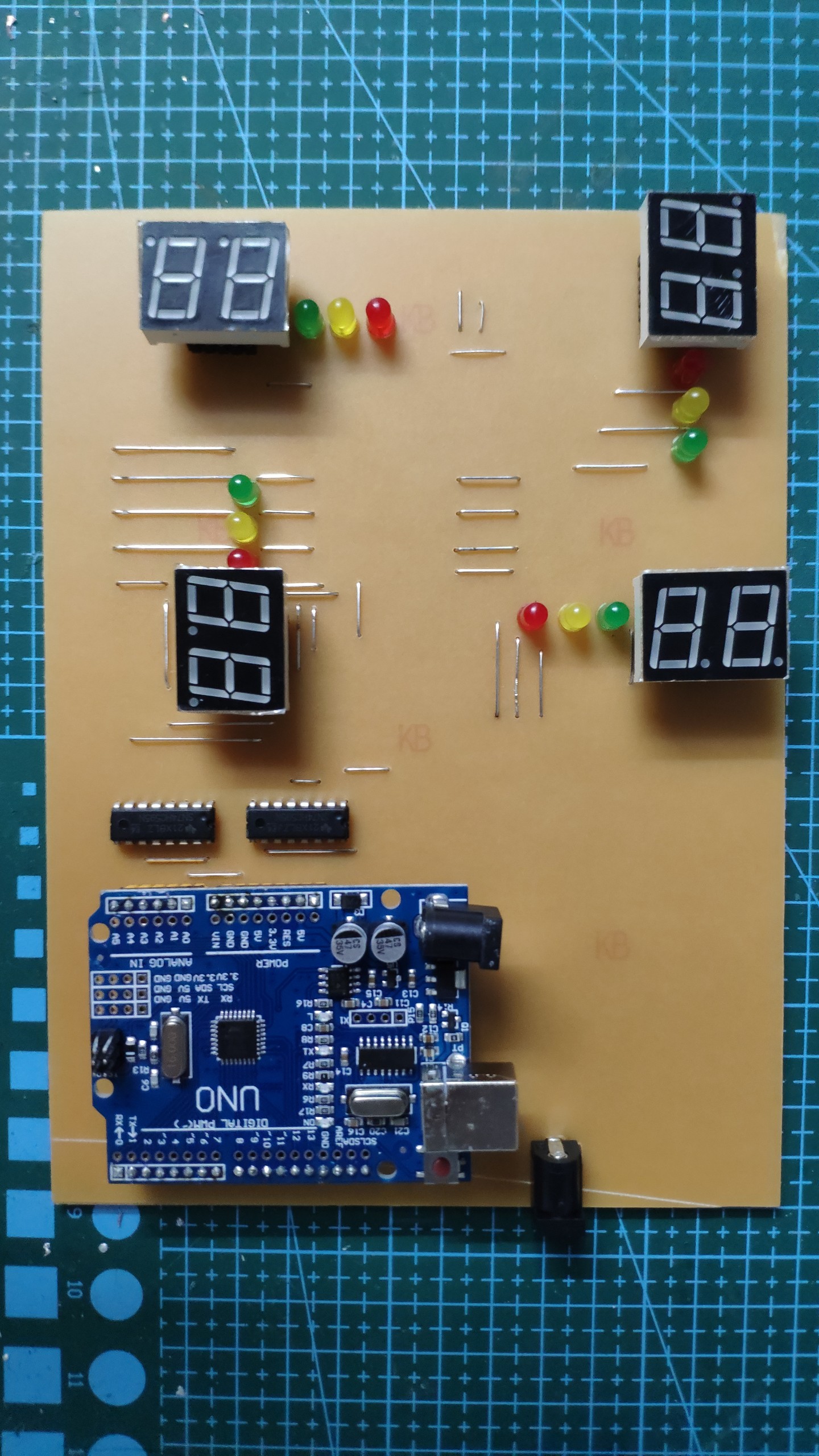

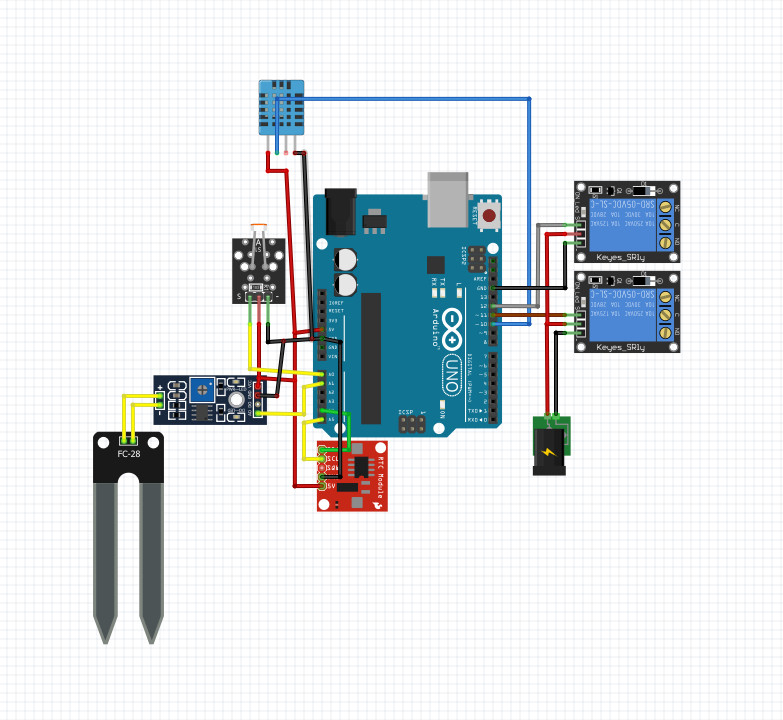

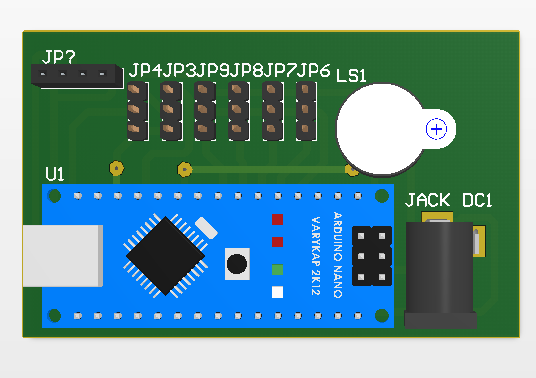

Bộ DIY Bơm Nước Tưới Cây Tự Động XH-M214 Cảm Biến Đo Độ Ẩm Đất Có Màn Hình Hiển Thị

139.000₫

178.000₫

-

22%

LED Công Suất Cao - Mắt LED Siêu Sáng COB 10W 20W 30W 50W 100W Hai Màu Lựa Chọn

22.500₫

35.000₫

-

36%

Bút Hàn Thiếc Mini Pin Lithium Không Dây 5V 8-15W Cổng Sạc Type-C Màu Bạc Sang Trọng

199.000₫

240.000₫

-

17%

Cáp Sạc Siêu Nhanh PD3.1 Tối Đa 240W Type-C to Type-C Truyền Dữ Liệu Tốc Độ Cao 480Mbps

99.000₫

120.000₫

-

18%

Led Quay 3D HOLOGRAM 1 Cánh 11cm Để Bàn Màn Hình Led Quảng Cáo, Trình Chiếu Độc Đáo

550.000₫

750.000₫

-

27%

Đèn Pin 3 Led SP7480 Uốn Dẻo Kéo Dài Có Nam Châm Từ Tính Nhặt Ốc Vít Chìa Khóa 560MM

72.000₫

84.000₫

-

14%

Đế Sạc Nhanh Không Dây QC3.0 Tối Đa 15W Siêu Mỏng Có Đèn Led Báo Trạng Thái

90.000₫

119.000₫

-

24%

Điện trở/Tụ điện/Cuộn cảm

- Điện Trở

![[Kiểu 1 Dài] Chân Đế Và Chân Ấm Siêu Tốc](http://bizweb.dktcdn.net/thumb/large/100/408/906/products/kieu-1-dai-chan-de-va-chan-am-sieu-toc-1.jpg?v=1617242950123)